# DESIGN OF ADVADVANCED ENCRYPTION STANDARD (AES) BASED RIJINDAEL ALGORITHM

J.Aarthi,

Electronics and Communication Engineering, Jayaram College of Engineering and Technology, Trichy Mail Id: <u>aarthirachagan@yahoo.com</u>

**Abstract** - Advanced standard encryption standard is mainly used for various security applications. Application specific integrated circuit (ASIC) with cryptographic algorithm is generate the efficient security levels for various applications. Rijindael algorithm works with encryptions and decryptions. Encryption is transform the transformations from plain text into cipher text and decryption are performs the reverse function of encryption. Mix column and inverse mix column is one of the complicate process to perform the encryptions and decryptions. In general, there are required number of the logical elements is comparatively high for the mix column and inverse mix column process. To provide the efficient logical elements for the mix column, the enhanced inverse mix column is proposed in this paper. These works improve the logical elements utilizations as well as the power optimizations. The enhanced mix column is produce the efficient Area, Delay and Power(ADP) products for the both encryption and decryptions.

**Keywords** - Advanced Standard Encryption (AES), Substitution Bytes(S-Box), Application-Specific-Integrated-Circuit (ASIC), Area, Delay, Power (ADP).

# **1. Introduction**

To protect the classified information, the symmetric block cipher is utilized for advanced encryption standard. For rijndael algorithm, there three size of bits is used for operations such as 128 Bits, 192 bits and 256 bits. Daemon implement the rijndael algorithm with 32 bit of the data blocks to provide efficient executions of the algorithm. Multiplicative masking and the Boolean masking is the main representatives of the AES algorithm. Composite S-Box is used to reduce the hardware utilizations and power utilizations as well as it improve the mix column transformations. Enhance mix column with composite s-box is evaluated and analyzed in terms of VLSI factors such as Area, Delay and Power.

#### 2. Related Works

Application specific integrated circuit(ASIC) with cryptographic algorithm is provide better security levels for various applications [1] described the AES Algorithm with efficient Mix column transformations.. Byte level representations are performed for standard operations. Galois field with polynomial is used to assume the bytes of the representations. AES standard

hardware implementation is high for the decryption process. To reduce the complexity of the both encryption and decryption is performed by the fixed coefficient technique. [2] presented the storage network for masked AES for reduce the utilizations of the storage network. For satellite communications and security applications, the AES can be used for security applications. Pipelining architecture is improve the speed of the architecture and also for security applications. Application specific integrated circuit(ASIC) with cryptographic algorithm is provide better security levels for various applications. [4] described the incorporation of wave pipelined techniques into composite S-Box and AES architectures. For every round of the operations, the wave pipeline technique is used to provide the efficient S-Box. Clock gating technique is used for the implementations; these techniques minimize the delay as well as the area. The field information is mainly depending on the byte representations.[5] explained the Sub bytes transformations. For the sub bytes transformations, there is no need for the LUTs and field of the data path. Decryption is retrieving the given input information in final stage.

#### 3. Rijndael Algorithm

- ' -

Rijndael algorithm is used for the AES method for the security purpose to provide efficient secured information data from the decryption process. AES is depend on Rijndael algorithm choose for data encryption standard by National Institute of Standards and Technology (NIST) in 1997. It performs data blocks of fixed size by cipher keys of length 128, 196 and 256 bits . AES-128 bit cipher keys are mainly used for encryption and decryption. Encryption side of AES can operate the 4 discrete transformations in particular order like S-Box, Shift Rows, MixColumn and Add Round Key. There are Three numbers of rounds have to be processed in order of 10, 12 and 14 for AES-128, AES-196 and AES-256 bits respectively. S-Box is provided by taking multiplicative inverse of data input in the finite Galois Field GF (2<sup>8</sup>) and it followed by an affine transformation. The irreducible polynomial of data input is represented as follows:

$$m(z) = z^8 + z^4 + z^3 + z + 1 \qquad (I)$$

.The matrix multiplication of MixColumn of AES is derived as below,

| <i>s</i> <sub>0,c</sub> | <b>[</b> 02 | 03 | 01 | 01] [S <sub>0,c</sub> ]                                                                                                              |      |

|-------------------------|-------------|----|----|--------------------------------------------------------------------------------------------------------------------------------------|------|

| s' <sub>1,c</sub>       | _ 01        | 01 | 03 | $01   S_{1,c}$                                                                                                                       | (II) |

| $s'_{2c}$               | 01          | 01 | 02 | 03 <i>S</i> <sub>2,c</sub>                                                                                                           | (11) |

| $S_2^{\prime}$          | L03         | 01 | 01 | $ \begin{bmatrix} 01\\01\\s_{1,c}\\s_{2,c}\\s_{3,c} \end{bmatrix} \begin{bmatrix} s_{0,c}\\s_{1,c}\\s_{2,c}\\s_{3,c} \end{bmatrix} $ |      |

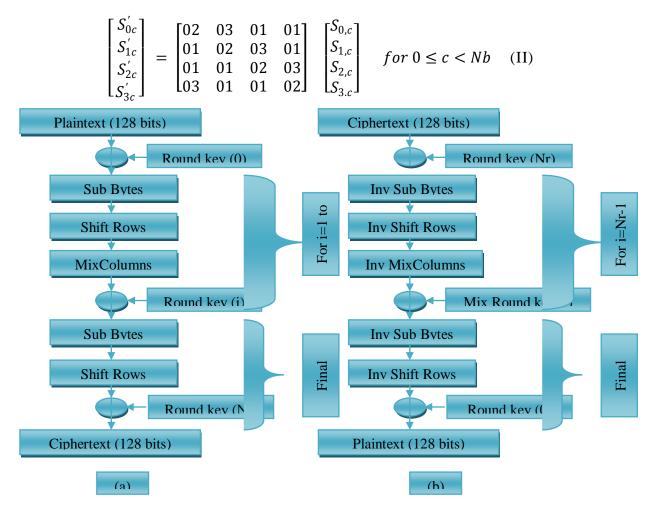

Add Round Key function can be processed in a 10 rounds of transformations can be performed, since here AES-128 bit length is considered for both input and output. The standard flow chart of AES encryption and decryption is analyzed in fig. 1.

Matrix multiplication of Inv MixColumn of AES is derived as below,

| $s_{0,c}$<br>$s_{1,c}'$ | 0 <i>e</i><br>09 | 0 <i>b</i><br>0e | 0d<br>0b   | $ \begin{bmatrix} 09\\0d\\0b\\02 \end{bmatrix} \begin{bmatrix} s_{0,c}\\s_{1,c}\\s_{2,c}\\s_{3,c} \end{bmatrix} $ | (III) |

|-------------------------|------------------|------------------|------------|-------------------------------------------------------------------------------------------------------------------|-------|

| $S_{2,c}$               | 0d               | 09               | 0 <i>e</i> | $0b \mid s_{2,c}$                                                                                                 | ()    |

| ,<br>                   | L0b              | 01               | 01         | $02[s_{3,c}]$                                                                                                     |       |

#### 4. General Inverse Mix-Column Transformation

The Mix-Column transformation performs on the State column-by-column, each column as a four term polynomial considered as polynomials over GF  $(2^8)$  and multiplied by modulo  $z^4+1$  with a fixed polynomial x (n) is given by,

$$z(n) = \{03\}_{z}^{3} + \{01\}_{z}^{2} + \{01\}_{z} + 02$$

(I)

This can be written as a, s' (z) = z (n)\*s (z). These can be illustrated as,

Fig. 1 AES ARCHITECTURE

Inverse mix column of the AES transformations illustrated as below,

$$z^{-1}(n) = \{0b\}z^3 + \{0d\}z^2 + \{09\}z + \{oe\}$$

(III)

(i.e)  $s'(z) = z^{-1}(n) \oplus s(z)$  The InvMix-Column matrix can be represented as below,

$$\begin{bmatrix} S_{0,c}'\\S_{1,c}'\\S_{2,c}'\\S_{3,c}' \end{bmatrix} = \begin{bmatrix} 0e & 0b & 0d & 09\\ 09 & 0e & 0b & 0d\\ 0d & 09 & 0e & 0b\\ 0b & 0d & 09 & 0e \end{bmatrix} \begin{bmatrix} S_{0,c}\\S_{1,c}\\S_{2,c}\\S_{3,c} \end{bmatrix} \quad for \ 0 \le c < Nb$$

(IV)

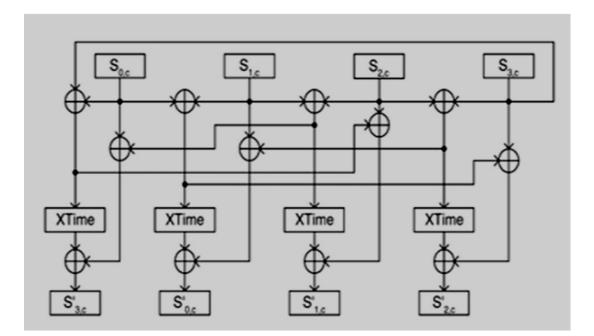

For Xtime multiplications, the standard polynomials input bytes are usedfor the multiplication process. These inputs are processed by using simple EX-OR gate operations that is by using usual logical exor gate, the bytes of input is performed. The required number of the logical gates are comparatively high for the inverse mix column process because of its word length. High utilizations of the logical gates is leads to the high area utilizations and also increase the power. To reduce the power as well as area, the inverse mix column circuits is proposed in this section.

**Fig. 2 Xtime Multiplcation**

#### 5. Proposed Enhanced Inv Mix-Column with Composite S-Box

To provide the efficient logical elements utilizations, the enhanced inverse mix column is proposed in this work. The proposed work is mainly focused to reduce the computational path of the equations. The proposed work is reducing the number of logical elements in the equations. Proposed equations are illustrated as below,

From equation 1,

$$\mathbf{S}'_{0,c} = \left(\{0e\} * \mathbf{S}_{0,c}\right) \oplus \left(\{0b\} * \mathbf{S}_{1,c}\right) \oplus \left(\{0d\} * \mathbf{S}_{2,c}\right) \oplus \left(\{09\} * \mathbf{S}_{3,c}\right)$$

(5)

$$\mathbf{S}'_{1,c} = \left(\{09\} \ast \mathbf{S}_{0,c}\right) \oplus \left(\{0e\} \ast \mathbf{S}_{1,c}\right) \oplus \left(\{0b\} \ast \mathbf{S}_{2,c}\right) \oplus \left(\{0d\} \ast \mathbf{S}_{3,c}\right) \tag{6}$$

$$\mathbf{S}'_{2,c} = \left(\{0d\} \ast_{\mathbf{S}_{0,c}}\right) \oplus \left(\{09\} \ast_{\mathbf{S}_{1,c}}\right) \oplus \left(\{0e\} \ast_{\mathbf{S}_{2,c}}\right) \oplus \left(\{0b\} \ast_{\mathbf{S}_{3,c}}\right) \tag{7}$$

$$\mathbf{S}'_{3,c} = \left(\{0b\} \ast \mathbf{S}_{0,c}\right) \oplus \left(\{0d\} \ast \mathbf{S}_{1,c}\right) \oplus \left(\{09\} \ast \mathbf{S}_{2,c}\right) \oplus \left(\{0b\} \ast \mathbf{S}_{3,c}\right)$$

(8)

Further, equation (5) to (8), can be simplified as

$$s'_{0,c} = \left[ \left( \{09\} *_{S_{0,c}} \right) \oplus \left( \{04\} *_{S_{0,c}} \right) \oplus \left( \{02\} *_{S_{0,c}} \right) \oplus _{S_{0,c}} \right] \\ \oplus \left[ \left( \{09\} *_{S_{1,c}} \right) \oplus \left( \{02\} *_{S_{1,c}} \right) \right] \oplus \left[ \left( \{09\} *_{S_{2,c}} \right) \oplus \left( \{04\} *_{S_{2,c}} \right) \right] \\ \oplus \left[ \left( \{09\} *_{S_{3,c}} \right) \right]$$

(9)

$$s'_{1,c} = [(\{09\} * s_{0,c})] \oplus [(\{09\} * s_{1,c}) \oplus (\{04\} * s_{1,c}) \oplus (\{02\} * s_{1,c}) \oplus s_{1,c}] \\ \oplus [(\{09\} * s_{2,c}) \oplus (\{02\} * s_{2,c})] \oplus [(\{09\} * s_{3,c}) \oplus (\{04\} * s_{3,c})] \quad (10) \\ s'_{2,c} = [(\{09\} * s_{0,c}) \oplus (\{04\} * s_{0,c})] \oplus [(\{09\} * s_{1,c})] \\ \oplus [(\{09\} * s_{2,c}) \oplus (\{04\} * s_{2,c}) \oplus (\{02\} * s_{2,c}) \oplus s_{2,c}] \\ \oplus [(\{09\} * s_{3,c}) \oplus (\{02\} * s_{3,c})] \quad (11) \\ s'_{3,c} = [(\{09\} * s_{0,c}) \oplus (\{02\} * s_{0,c})] \oplus [(\{09\} * s_{1,c}) \oplus (\{04\} * s_{01c})] \\ \oplus [(\{09\} * s_{2,c}) \oplus (\{09\} * s_{3,c}) \oplus (\{04\} * s_{3,c}) \oplus (\{02\} * s_{3,c}) \oplus (s_{3,c})] \\ \oplus [(\{09\} * s_{2,c}) \oplus (\{09\} * s_{3,c}) \oplus (\{04\} * s_{3,c}) \oplus (\{02\} * s_{3,c}) \oplus (s_{3,c})] \\ \oplus [(\{09\} * s_{2,c}) \oplus (\{09\} * s_{3,c}) \oplus (\{04\} * s_{3,c}) \oplus (\{02\} * s_{3,c}) \oplus (s_{3,c})] \\ \oplus [(\{09\} * s_{2,c}) \oplus (\{09\} * s_{3,c}) \oplus (\{04\} * s_{3,c}) \oplus (\{02\} * s_{3,c}) \oplus (s_{3,c}) \oplus (s_{$$

From equation (9) to (12), it is clear that multiplication of source signals with  $\{09\}$ ,  $\{04\}$  and  $\{02\}$  are redundantly used for calculation of Inv MixColumn. This common resources are represented are as follows,

$$c1_{09} = \{09\} * s_{0,c} \qquad c1_{04} = \{04\} * s_{0,c} \qquad c1_{02} = \{02\} * s_{0,c}$$

$$c2_{09} = \{09\} * s_{1,c} \qquad c2_{04} = \{04\} * s_{1,c} \qquad c2_{02} = \{02\} * s_{1,c}$$

$$c3_{09} = \{09\} * s_{2,c} \qquad c3_{04} = \{04\} * s_{2,c} \qquad c3_{02} = \{02\} * s_{2,c}$$

$$c4_{09} = \{09\} * s_{3,c} \qquad c4_{04} = \{09\} * s_{3,c} \qquad c4_{02} = \{02\} * s_{4,c}$$

The hardware complexity of Inv MixColumn can be absolutely reduced, when sharing these resources to all numerical calculation of Inv MixColumn. Further the equation (9) to (12) an be simplified as,

$$s'_{0,c} = (c_{1_{09}} \oplus c_{1_{04}} \oplus c_{1_{02}} \oplus s_{0,c}) \oplus (c_{2_{09}} \oplus c_{2_{02}}) \oplus (c_{3_{09}} \oplus c_{3_{02}}) \oplus (c_{4_{09}})$$

(13)

$$s'_{1,c} = (c_{1_{09}}) \oplus (c_{2_{09}} \oplus c_{2_{04}}) \oplus (c_{2_{02}} \oplus s_{1,c}) \oplus (c_{3_{09}} \oplus c_{3_{02}}) \oplus (c_{4_{09}} \oplus c_{4_{04}})$$

(14)

$$s'_{2,c} = (c_{1_{09}} \oplus c_{1_{04}}) \oplus (c_{2_{09}}) \oplus (c_{3_{09}} \oplus c_{3_{04}} \oplus c_{3_{02}} \oplus s_{2,c}) \oplus (c_{4_{09}} \oplus c_{4_{02}})$$

(15)

$$s'_{3,c} = (c_{1_{09}} \oplus c_{1_{04}}) \oplus (c_{2_{09}} \oplus c_{2_{04}}) \oplus (c_{3_{09}}) \oplus (c_{4_{09}} \oplus c_{4_{04}} \oplus c_{4_{02}} \oplus s_{3,c})$$

(16)

State bytes T<sub>9</sub> and T<sub>4</sub> are evaluated by as follows. Multiplication of {09} with state-byte,  $t_7 = 0$ ,  $t_6 = b_7$ ,  $t_5 = b_6 \oplus b_7$ ,  $t_4 = b_5 \oplus b_6$ ,  $t_3 = b_5 \oplus b_7$ ,  $t_2 = t_5$ ,  $t_1 = t_4$ ,  $t_0 = b_5$ Multiplication of {04} with state-byte,

$$t_7 = 0$$

,  $t_6 = 0$ ,  $t_5 = b_7$ ,  $t_4 = b_7 \oplus b_6$ ,  $t_3 = b_6$ ,  $t_2 = b_7$ ,  $t_1 = t_4$ ,  $t_0 = b_6$

## 6. Experimental Results

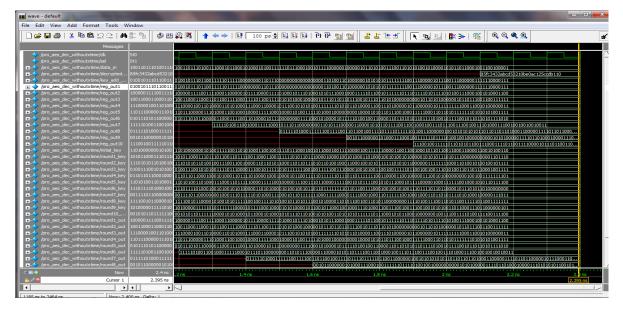

In this work, the enhanced inverse mix column with composite S-Box design is analyzed and evaluated in Modelsim XE by Verilog HDL Language and these synthesis results are estimated by Xilinx ISE Design suite. The hardware implementations of the AES encryption and decryption are implemented in Virtex-4 XC4VLX15 device through Xilinx ISE tool. Simulation result of Encryption by using Minimized Composite S-Box and Enhanced Inv Mix Column are shown in Fig.5 and Simulation result of Decryption by using Minimized S-Box and Enhanced Inv Mix Column are shown in Fig.6

| Edit View Add Format                                       | Tools Window               |                        |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

|------------------------------------------------------------|----------------------------|------------------------|-----------------|----------------------|-----------|--------------|-----------------|----------------|------------------|--------------|-----------------|------------------|-----------------|------------------|--------|

| ) 🛹 🗖 🛷 L V 🗈 🙉 🐑                                          | C 1 M & %                  | 🐟 🕮 🚜 🕱                | A day when      | 1.000                | 0. mm 📥 [ | TH THE THE   | 71 71 100       | mul 1+         |                  |              | out time the    |                  |                 |                  |        |

|                                                            | 10000   Martin 201-00 1228 | 400 End 444 End        |                 | 1 10                 |           |              | 1.0.0           | [] <del></del> |                  |              |                 | 1 20m  ] 🛰       | ~ ~ ~           |                  |        |

| Messages                                                   |                            |                        |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/clk                                           | St0                        |                        |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/sel                                           | StO                        |                        |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/data_in                                       |                            | 1000010111111100       | 0011010000110   | 01010101010111       | 100110101 | 101001100100 | 001000010111    | 11000001010    | 1100000100100    | 10111001100  |                 |                  |                 |                  |        |

| /aes_top_enc/encrypted_data<br>//aes_top_enc/key_add_out   |                            | 10 10 1 1 10 100000 10 |                 |                      |           |              |                 |                |                  |              |                 | a7ee25e0416a     | 2354a15b1321    |                  |        |

| <pre>/aes_top_enc/key_add_out //aes_top_enc/reg_out1</pre> | 10101110100000100          | 1010111010000010       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 | _ <mark>.</mark> |        |

| <pre>/acs_cop_enc/reg_out2</pre>                           |                            | 0 10000 100 1 1 1 1000 |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| <pre>/aes_top_enc/reg_out3</pre>                           | 00010011001011010          | 0001001100101101       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes top enc/reg out4                                      |                            | 000 10 100000 10 1 10  |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/reg_out5                                      |                            | 1000110110101011111    |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/reg_out6                                      | 1001001110000100           | 1001001110000100       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/reg_out7                                      | 1110000001010101010        |                        | (111000)        | 000 10 10 10 10 10 1 | 100000001 | 00001110110  | 0000 10 1000 10 | 111100010111   | 100100011000     | minomone     | 011101010101100 | 000111100011     | 1010110111110   | 00100            |        |

| /aes_top_enc/reg_out8                                      | 11100010100111100          |                        |                 |                      | (11       | 11000101001  | 11001101100     | 00011110101    | 11 111000 1111   | 00011110110  | 1010100100111   | 1111 10 10 10 1  | 111100100101010 | 00110011111111   | 0      |

| /aes_top_enc/reg_out9                                      | 0100000110001001           |                        |                 |                      |           |              |                 |                |                  |              |                 |                  | 0000100010110   | 0 10 00000 110   | 10     |

| /aes_top_enc/initial_key                                   |                            | 001010110111110        |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round1_key                                    |                            | 1010000011111010       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round2_key                                    |                            | 1111001011000010       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round3_key<br>/aes_top_enc/round4_key         | 00111101100000000          | 0011110110000000       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

|                                                            |                            | 1110111101000100       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round5_key /aes_top_enc/round6_key            |                            | 01101101100010001      |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round7_key                                    |                            | 01001110010101000      |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round8_key                                    |                            | 11101010101010010      |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round9_key                                    |                            | 1010110001110111       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round10_key                                   |                            | 1101000000010100       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round1_out                                    | 0100001001111000           | 0100001001111000       | 1101111001101   | 111110011011         | 010001100 | 0001111011   | 001100010111    | 01001100111    | 0110101001100    | 1001000001   | 1010010100100   | 1101110          |                 |                  |        |

| /aes_top_enc/round2_out                                    | 0001001100101101(          | 0001001100101101       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round3_out                                    | 0001010000010110           | 0001010000010110       | 1011011010100   | 011001110101         | 000110010 | 01001101011  | 000100111000    | 00001010000    | 000 100 1000 100 | 01111011000  | 1100010000011   | 0001101          |                 |                  |        |

| /aes_top_enc/round4_out                                    | 100011011010111110         | 100011011010101111     |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round5_out                                    |                            | 1001001110000100       |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round6_out                                    | 1110000001010101010        | 111000                 | 000101010101011 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

| /aes_top_enc/round7_out                                    | 11100010100111100          |                        |                 | (111000              | 10100111  | 10011011000  |                 |                |                  |              |                 |                  |                 | 10 111 1000 1110 |        |

| /aes_top_enc/round8_out                                    | 0 100000 1 1000 100 1      |                        |                 |                      |           |              | 010000011000    | 0011000101     |                  |              |                 |                  |                 | 01001111000010   | 01     |

| /aes_top_enc/round9_out                                    | 1100110001110110(          |                        |                 |                      |           |              |                 |                | 1100110001       | 110110011010 | 111110010001    | 000 10 10 100 10 | 1111001011000   | 1,100010001110   |        |

| Now                                                        | 2.4 ns                     | 1.2 ms                 |                 | 1.4 ns               |           | 1.0          | ins             |                | L8 ns            |              |                 |                  | 2.2 ns          |                  | 2.4 ms |

| Cursor 1                                                   | 2.277 ns                   |                        |                 |                      |           |              |                 |                |                  |              |                 |                  | 2               | 277 ns           |        |

| Þ                                                          | 4 1                        | Z                      |                 |                      |           |              |                 |                |                  |              |                 |                  |                 |                  |        |

Fig.5 Simulation result of Encryption by using Minimized Composite S-Box and Enhanced Inv MixColumn

Fig.6 Simulation result of Decryption by using Minimized Composite S-Box and Enhanced Inv MixColumn

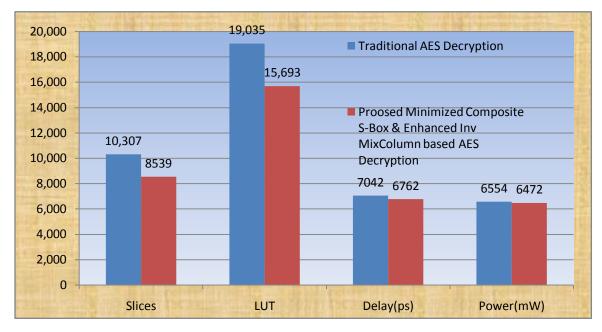

Fig.7 Comparisons for the existing and proposed AES Encryption and Decryption

### 7. Conclusion

In this work, the enhanced inverse mix column with composite S-Box design is simulated by hardware description language and these synthesis results are analyzed by Xilinx ISE. Proposed Composite S-Box and Enhanced Inv Mix Column transformations are implemented into AES encryption and AES decryption process respectively. The proposed design is provide 17% reduction of the slices and LUTs and 3% of the delay and efficient power consumptions. Proposed work performs for applications security Systems, Space and terrestrial communications.

### REFERENCES

- [1] Viktor Fischer, Milos Drutarovsky, Pawel Chodowiec and Francois Gramain, "InvMixColumn Decomposition and Multilevel Resource Sharing in AES Implementations" IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 13, No. 8, 2005.

- [2] M. Anitha Christry and S. Sridevi Sathya Priya, "Design of Low Power Mixcolumn in Advanced Encryption Standard Algorithm" International Journal of Scientific & Engineering Research, Vol. 5, Issue. 4, pp: 64-68, 2014.

- [3] Anitha, S., and Suganya, M., 2015. "Area optimized in storage area network using Novel Mix column Transformation in Masked AES" International Journal of Engineering Trends and Technology (IJETT), Vol. 20, No. 6, pp: 275-282.

- [4] M. Senthil Kumar and S. Rajalakshmi, "Incorporation of Wave Pipelined Techniques into Composite S-Box and AES Architectures" *Research Journal of Applied Sciences*, *Engineering and Technology* (RJASET), Vol. 8, No. 15, pp: 1717-1723, 2014.

# International Journal of MC Square Scientific Research Vol.6, No.1 Nov 2014

[5] Sandyarani, K., and Nirmal kumar, P., 2014. "Design of high speed AES-128 using Novel Mix Column Transformation and Sub Bytes" Journal of Computer Applications (JCA), Vol. 7, Issue. 2, pp: 57-60.